Integrated Circuit Mass

How Much does a Chip Weigh?

CMOS (Complimentary Metal Oxide Semiconductor) integrated circuit chips are made N type and P type MOS field effect transistors, wiring, insulators, on top of a silicon substrate. The zoo of devices on all varieties of integrated circuits includes bipolar transistors, diodes, capacitors, loop inductors, diffused and thin-film resistors, sometimes even special sensors like avalanche photodiodes. However, almost everything we do with server sky will involve advanced-process CMOS, with some DRAM ( Dynamic Random Access Memory ) using stack capacitors and some flash (block rewritable) EEPROM ( Electrically Eraseable Programmable Read Only Memory, which writes information by trapping charges in the insulators of MOS gates.

|

These are all planar processes produced by photolithography. All structures are made by deposition and etching of materials, and are typically very thin, a few micrometers. High power integrated circuits, such as 150 watt microprocessors and GPUs, are somewhat thicker, because the uppermost layers of interconnect metal are thick and low resistance to handle up to 100 amps of power. The lower signal handling metal layers are thin and optimized for low capacitance wires, perhaps half as thick as they are wide (a fraction of a micrometer). |

Server sky chips will use low power varieties of these advanced processes, with fewer metal layers and no fat upper layers because each chip will be small and use milliamps rather than amps. We can expect the thickness of the active layers of chips to be less than five microns thick.

Integrated circuit chips are built on large wafers, 30 centimeters or more in diameter. The wafers are typically 750 μm (micrometers) thick for mechanical stiffness during manufacturing. After the planar circuitry is completed, the wafers are "backlapped", ground down on the back side to make them thinner. Then they are sawn into individual die ( == chips ). The backlapping is a coarse grinding process, and variation in the process limits the thinness of the resulting die, but 50 μm thick is a typical result, good enough for cell phones and other volume-constrained products. The die can be made much thinner, as low as 20 μm or even 7.5 μm, for attachment to paperthin substrates in applications such as RFID tags. Such paperthin die are more flexible and more resistant to fracture, and the processes for making thin chips reliably will (hopefully) be widespread and very inexpensive when thinsats are produced by the billions.

The density of silicon is 2.33 g/cm3, so a 20 μm layer of processed silicon weighs about 4.7 mg/cm2, or about 20 square meters per kilogram (note: the silicon would be partly transparent, too thin for solar cells). A 300 millimeter wafer thinned to 20 μm weighs 3.5 grams and has an area of 700 cm2. Assuming a 2x markup for profit and yield loss $5000 processor wafer costs $15 per cm2 or about $3M per kilogram thinned to 20 μm . A $1600 memory wafer costs $5 per cm2 or about $1M per kilogram thinned.

|

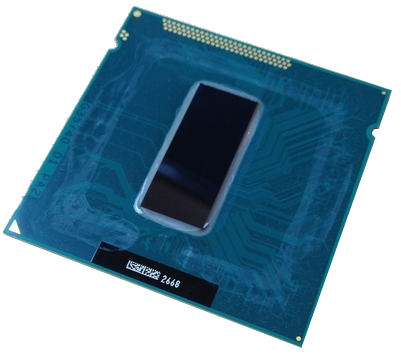

This is an Intel Ivy Bridge CPU, with 4 processor cores and 1.4 billion transistors, attached upside down to a package. The chip is 1.6 cm2, and probably thinned down below 750 μm to improve thermal conductivity. If this die was thinned to 200 μm, the silicon would weigh perhaps 85 milligrams. If it was thinned to 50 μm, 34 milligrams, about 8 milligrams and 0.4cm2 per processor. A large Google data center might contain a million processors; about 2 kilograms of active CPU silicon - embedded in tons of substrate and packaging, and thousands of tons of circuit boards, racks, wiring and cooling water plumbing. |

|

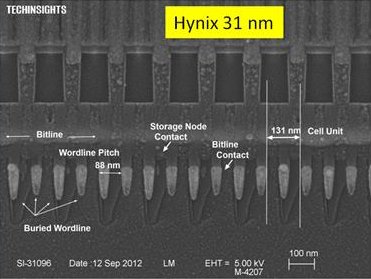

Dynamic Random Access Memory Hynix 62x93nm (31nm 6F?) DRAM cell. A gigabyte of RAM has an area of 0.6 cm2, including some periphery and error-correction processing. At 20μm thick, that is 3 mg/GiB, or 330TiB/kg, 2.9E15 transistors costing $1M after yield loss and profit |

|

Solid State Flash Memory. Cross section of a 27nm Samsung NAND flash array. Intel and Micron offer a 25 nm, 64 gigabit, 1.31 cm2 3 level flash memory. At $5/cm2, that is $820/TiB. Thinned to 20 μm, that is 800mg/TiB, 1.2PiB/kg, 3.6E15 transistors/kg. |

Memory will have additional logic to do error correction after access and before refresh. It will likely be optimized to run at higher power efficiency and lower speed than terrestrial applications like desktop CPUs |

|

|

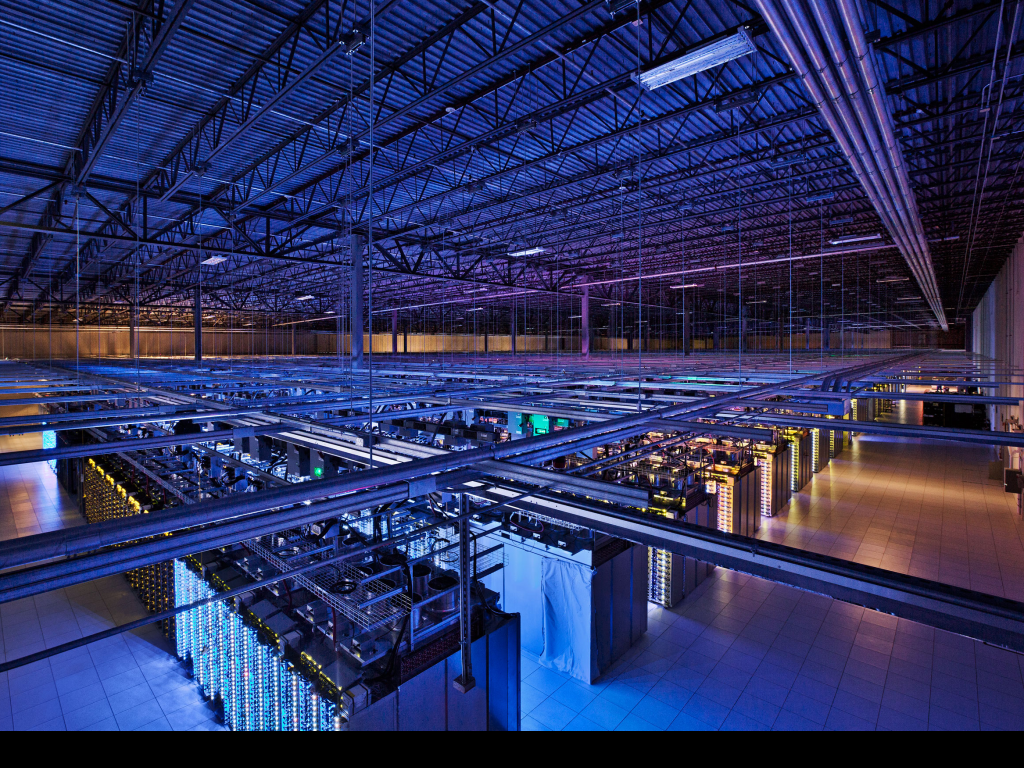

Google Data Center - est. 110 lb/ft2 including structure, power transformers, plumbing and rooftop chillers, 200,000 sq ft (two buildings plus auxiliary structures), 1 million kilograms. |

A 256 core, 1 TiB flash, 64 GiB dram processor array at $10/g launch cost, active silicon only, NOT including thinsat substrate, solar cell, wiring, etc:

component |

mass |

total area |

total mass |

chip cost |

launch cost |

256 processors |

0.47mg/proc |

25.6 cm2 |

120 mg |

$384.00 |

$1.20 |

512 GiB flash |

700mg/TiB |

75.0 cm2 |

350 mg |

$250.00 |

$3.50 |

64 GiB dram |

0.8mg/GiB |

9.6 cm2 |

45 mg |

$48.00 |

$0.45 |

Total |

|

110.2 cm2 |

515 mg |

|

$5.15 |

If this represents the capability of one thinsat, and an array of 7842 thinsats weighs 39kg, then multiply the above compute power by 7942 for a silicon launch cost of $40K and a thinsat launch cost of $390K, including power supply and radio ground link. Arrays share flash storage, so the flash memory capacity of the entire array would be 3.9 petabytes.

Intra-array bandwidth is limited, so frequently accessed items will be stored on many thinsats, some items cached in flash memory on all of them. Access to specific information items will follow a long tail power law distribution, with a small percentage of all stored information accounting for a large percentage of downlink traffic. Some rarely used items will be bit compressed and stored in only a few arrays, perhaps even on the ground. As the array count M288 approaches environmental limits, some of the rarely-used information may be stored in arrays in higher orbits producing less light pollution.

Alternative: A Slimmer Thinsat with Multipurpous chips

We will need 1000 radio power amplifiers, perhaps 4 per chip, but we do not need 250 processors. Imagine that we populate the thinsat with 250 die, each driving 4 radios and connecting to 4 nearest neighbors in a grid with high speed low voltage differential buses, but a mix of processors, flash, and DRAM. First, let's cut the flash way back - we have about 8000 thinsats in an array; if we want to store a ten thousand hours of video per array, at 10 GiB per hour of video, that is 100 PiB, or 128 GiB per thinsat. Still a lot. Early arrays may produce only one gigabit per second, this is mostly a distribution issue, we don't need that much processing per thinsat. Lets assume we can get by with a mere 16 processors per thinsat, with 8 redundant spares for failure (and normally powered down). RAM? Same deal. We will divide compute jobs up among the whole array, we can operate the processors on one thinsat SIMD or from small programs. Let's cut the total RAM per thinsat down to 8GB (with 4 redundant GB), and assume that 64 TB per 8000 thinsats is plenty. So, how much area is that?

Second Estimate |

|||||

component |

mass |

total area |

total mass |

chip cost |

launch cost |

24 processors |

0.53mg/proc |

2.4 cm2 |

13 mg |

$36.00 |

$0.13 |

128 GiB flash |

800mg/TiB |

18.8 cm2 |

100 mg |

$63.00 |

$1.00 |

12 GiB dram |

3mg/GiB |

1.8 cm2 |

36 mg |

$9.00 |

$0.09 |

Total |

|

23.0 cm2 |

149 mg |

$108.00 |

$1.24 |

If we divide 2300 mm2 by 250 chips, that works out to about 9.2 mm2, a hair over 3 mm on a side. Let's add some periphery and drivers to that 0.1mm on a side is plenty - and we get 3.2 mm on a side. Rounding, that's 26 processor chips, 204 flash chips, and 20 dram chips per thinsat, all 3.2x3.2 mm with identical I/O. 10.24 mm2 per die. Extra multipurpose pins on each chip can be programmed to connect to SAW resonators for timing, electrochromic thrusters, or other functions.

7842 Thinsats |

per Thinsat |

per Array |

|

Silicon Area |

25.6 cm2 |

20.33 m2 |

|

Silicon Mass |

120 mg |

0.95 kg |

|

Chip Cost |

$108 |

$846K |

|

Est Thinsat Mfg Cost |

$42 |

$329K |

|

5g Thinsat Launch Cost |

$50 |

$392K |

|

Deploy Bus cost |

|

$50K |

|

Total Cost |

|

$2M |

WAG!!! |

Very Small Chips

Among the smallest manufactured chips are Hitachi's "µ-Chip"s.

year |

width |

length |

thick |

Process |

|

2001 |

400µm |

400µm |

?? |

?? |

|

2003 |

300µm |

300µm |

60um |

180nm |

|

2006 |

150µm |

150µm |

7.5µm |

?? |

|

2011 |

75µm |

75µm |

5.0µm |

|

No chip, a chip handling process instead |

2007 |

50µm |

50µm |

5.0µm |

90nm SOI |