Integrated Circuit Mass

How Much does a Chip Weigh?

CMOS (Complimentary Metal Oxide Semiconductor) integrated circuit chips are made N type and P type MOS field effect transistors, wiring, insulators, on top of a silicon substrate. The zoo of devices on all varieties of integrated circuits includes bipolar transistors, diodes, capacitors, loop inductors, diffused and thin-film resistors, sometimes even special sensors like avalanche photodiodes. However, almost everything we do with server sky will involve advanced-process CMOS, with some DRAM ( Dynamic Random Access Memory ) using stack capacitors and some flash (block rewritable) EEPROM ( Electrically Eraseable Programmable Read Only Memory, which writes information by trapping charges in the insulators of MOS gates.

|

These are all planar processes produced by photolithography. All structures are made by deposition and etching of materials, and are typically very thin, a few micrometers. High power integrated circuits, such as 150 watt microprocessors and GPUs, are somewhat thicker, because the uppermost layers of interconnect metal are thick and low resistance to handle up to 100 amps of power. The lower signal handling metal layers are thin and optimized for low capacitance wires, perhaps half as thick as they are wide (a fraction of a micrometer). |

Server sky chips will use low power varieties of these advanced processes, with fewer metal layers and no fat upper layers because each chip will be small and use milliamps rather than amps. We can expect the thickness of the active layers of chips to be less than five microns thick.

Integrated circuit chips are built on large wafers, 30 centimeters or more in diameter. The wafers are typically 750 μm (micrometers) thick for mechanical stiffness during manufacturing. After the planar circuitry is completed, the wafers are "backlapped", ground down on the back side to make them thinner. Then they are sawn into individual die ( == chips ). The backlapping is a coarse grinding process, and variation in the process limits the thinness of the resulting die, but 50 μm thick is a typical result, good enough for cell phones and other volume-constrained products. The die can be made much thinner, as low as 20 μm or even 7.5 μm, for attachment to paperthin substrates in applications such as RFID tags. Such paperthin die are more flexible and more resistant to fracture, and the processes for making thin chips reliably will (hopefully) be widespread and very inexpensive when thinsats are produced by the billions.

|

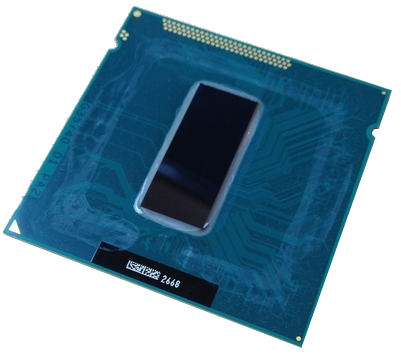

This is an Intel Ivy Bridge CPU, with 4 processors and 1.4 billion transistors, attached upside down to a package. The chip is 1.6 square centimeters, and probably thinned down from 750 μm to improve thermal conductivity. If this die was thinned to 200 μm, the silicon would weigh perhaps 85 milligrams. If it was thinned to 20 μm, 8.5 milligrams, about 2 milligrams per processor. A large Google data center might contain a million processors; about 20 kilograms of active silicon. |

RAM

Solid State Memory